I have the exact same setup and similar problem like this guy - Trigger error in Lab_2_1 - Embedded Security - NewAE Forum

Short summary

I am getting the “gain too low” error when using cw.capture_trace. But despite that it seems I can finish the UART triggers after clearing the error every time it appears? Really confused why the error appears.

My setup

- Notebook:

02 - Husky Triggers.ipynb(I only addedscope.errorsorscope.errors.clear()to retry some steps, sometimes that worked, see below) - Setup: CW Husky + CW308 UFO board + STM32F303 target (identical to his)

- CW version: latest master

534fe4881bb54723eb43df465cc54b406d9ccc4ffrom Mar 20 2023 (later than 5.7.0) on Linux

Errors encountered in 02 Husky Triggering demo for UART

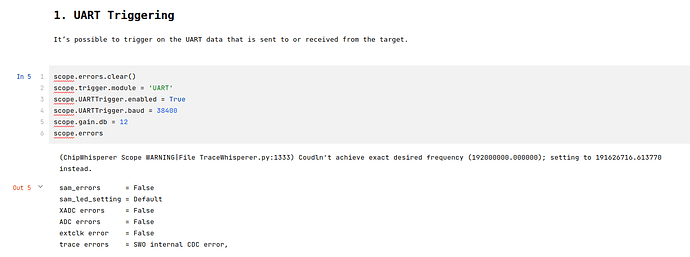

So the first hiccup in the demo is under “1. UART Triggering”

First running cell starting with scope.trigger.module = 'UART' throws a warning about imprecise frequency and “SWO imprecise CDC error”, running the cell second time works:

First run:

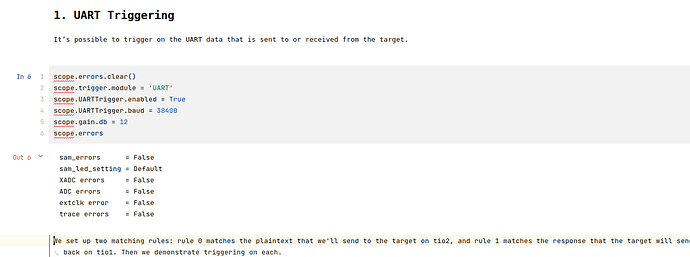

Second run of same cell, no error:

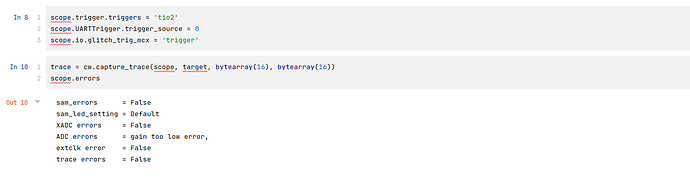

The capture_trace error

Now when we get to cell with race = cw.capture_trace(scope, target, bytearray(16), bytearray(16)), I am always getting “gain too low” error, even when repeating with clearing errors first:

Full output of print(scope) after that:

cwhusky Device

sn = 50203120374a38503230343138303037

fpga_buildtime = 3/2/2023, 21:35

fw_version =

major = 1

minor = 5

debug = 0

gain =

mode = low

gain = 59

db = 12.064220183486238

adc =

state = False

basic_mode = rising_edge

timeout = 2

offset = 0

presamples = 0

samples = 5000

decimate = 1

trig_count = 4

stream_mode = False

test_mode = False

bits_per_sample = 12

segments = 1

segment_cycles = 0

segment_cycle_counter_en = False

clip_errors_disabled = False

lo_gain_errors_disabled = False

errors = gain too low error,

clock =

clkgen_src = system

clkgen_freq = 7370129.87012987

adc_mul = 4

adc_freq = 29480519.48051948

freq_ctr = 338607

freq_ctr_src = extclk

clkgen_locked = True

adc_phase = 0

extclk_monitor_enabled = False

extclk_error = False

extclk_tolerance = 102.996826171875

trigger =

module = UART

triggers = tio2

io =

tio1 = serial_rx

tio2 = serial_tx

tio3 = high_z

tio4 = high_z

pdid = high_z

pdic = high_z

nrst = high_z

glitch_hp = False

glitch_lp = False

extclk_src = hs1

hs2 = clkgen

target_pwr = True

tio_states = (1, 1, 1, 0)

cdc_settings = bytearray(b'\x00\x00\x00\x00')

aux_io_mcx = high_z

glitch_trig_mcx = trigger

glitch =

enabled = False

mmcm_locked = False

num_glitches = 1

clk_src = target

width = 0

offset = 0

trigger_src = manual

arm_timing = after_scope

ext_offset = 0

repeat = 1

output = clock_xor

phase_shift_steps = 4592

ADS4128 =

mode = normal

low_speed = True

hi_perf = 2

LA =

present = True

enabled = False

clkgen_enabled = True

locked = True

clk_source = pll

trigger_source = glitch

oversampling_factor = 2

sampling_clock_frequency = 14740516.662597656

downsample = 1

capture_group = glitch

capture_depth = 0

trace =

present = True

enabled = True

errors = False

trace_synced = True

trace_mode = parallel

trace_width = 4

clock =

fe_clock_alive = True

fe_clock_src = target_clock

clkgen_enabled = True

fe_freq = 7370258.331298828

swo_clock_locked = True

swo_clock_freq = 14740516.662597656

capture =

trigger_source = trace trigger, rule #0

use_husky_arm = True

raw = True

rules_enabled = [0, 1]

rules = [{'rule': 0, 'patt': bytearray(b'\x00\x00\x00\x00\x00p00'), 'mask': bytearray(b'\x00\x00\x00\x00\x00\xff\xff\xff')}, {'rule': 1, 'patt': bytearray(b'\x00\x00\x00r7DF7'), 'mask': bytearray(b'\x00\x00\x00\xff\xff\xff\xff\xff')}]

mode = off

count = 0

max_triggers = 1

triggers_generated = 1

record_syncs = True

matched_pattern_data = 3030303030703030

matched_pattern_counts = [11, 0, 0, 0, 0, 0, 0, 0]

XADC =

status = good

current temperature [C] = 54.5

maximum temperature [C] = 56.7

user temperature alarm trigger [C] = 80.0

user temperature reset trigger [C] = 59.9

device temperature alarm trigger [C] = 89.9

device temperature reset trigger [C] = 59.9

vccint = 1.002

vccaux = 1.797

vccbram = 1.002

userio =

mode = trace

direction = 3

drive_data = 0

status = 508

LEDs =

setting = 0 (default, as labelled)

errors =

sam_errors = False

sam_led_setting = Default

XADC errors = False

ADC errors = gain too low error,

extclk error = False

trace errors = False

It seems I can finish the UART part of the demo and it looks like it works, but the “gain too low error” is confusing. Clearing the errors via scope.errors.clear() each time they appear seems to work, but really don’t understand what is going on here, what the error actually means.