Hi Everyone,

I am testing SHA-3 algorithm unprotected/protected on CW305 target. Facing some issue due to time drift of power traces.

Design details: Design is self-contained and require one pulse to run on-die PRNG to generate vectors and internal control signals for execution of back-to-back 1024 different input vectors for high throughput characterization without any external communication. Design is running at 10 MHz clock with 10% LUT utilization. FPGA is powered with USB connector.

Power traces: I am capturing 20db amplified power traces across X4 SMA using the external oscilloscope with trigger generated by FPGA on IO pins.

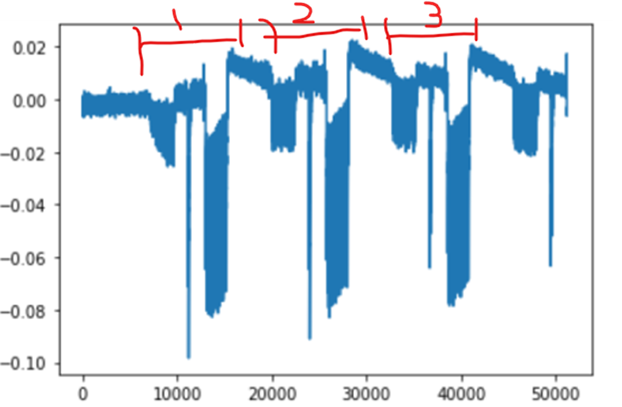

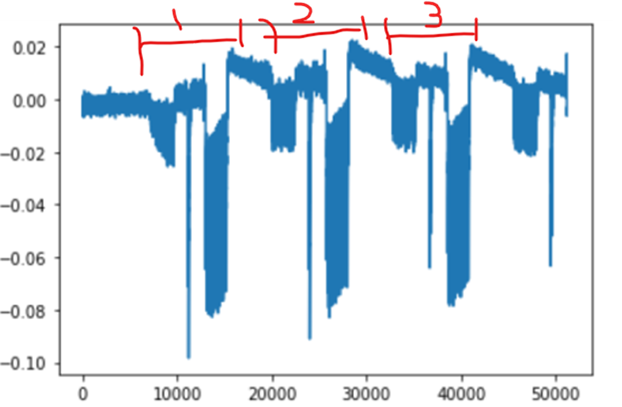

Issue: Some drift trend along time axis in the power waveform as per picture attached with marking as first three vectors. I need to avoid this as I am using these interleaved back-to-back traces for TVLA analysis. I am getting unexpected leakage in protected implementation.

All suggestions are welcome.

To me, “time drift” refers to a de-synchronization effect on the horizontal (time) axis, and what I see here is a drift on the vertical axis. Is this what you are talking about?

If you are indeed talking about time drift, I cannot make it out from this low-resolution screen shot. Ensure that you are capturing synchronously with the target clock, and consider adding some instrumentation to your target so that you can confirm that the actual length of each target operation is constant.

The vertical drift is a consequence of all the target components that have a time constant, along with the sudden change when your target goes from idle to active. You can try filtering or adjusting a delay between target operations such that the startup conditions of each operation are identical.

I hope this helps.

Thanks for your reply. Sorry about the confusion.

Indeed, i was referring to vertical drift as time passes. I understand that DUT on FPGA is going from idle to compute creating power current peak leading to power trace ringing/oscillation. I am not sure about the long delay in discharge settling to idle condition. Currently there is around 32 cycles gap (3.2 us) between each operation which seems enough.

Thank you very much for your suggestion. Can you elaborate more on filtering, are your referring to filtering traces with BP filter around operating frequency ?

thanks

I’ve not tried it but I was thinking that high-pass filtering may be helpful?

But my first choice would be to create identical starting conditions for each target operation.