You reference CW340_AES_test.ipynb, which sets (among other things) scope.clock.clkgen_src = 'extclk', yet the output above shows that you have clkgen_src set to “system” instead.

This is a problem because the FPGA target is set up to use a clock generated by the CW340 PLL. This clock is provided back to Husky so that it may sample synchronously with the target’s clock (that’s what clkgen_src = ‘extclk’ does). Here instead you have Husky set up to generate an ADC sampling clock that has no relation to the target clock. This explains why your traces don’t look so great.

Are you running cw340-luna-board/jupyter/CW340_AES_test.ipynb at main · newaetech/cw340-luna-board · GitHub properly and fully?

No, that’s not the recommended way to obtain measurements.

EIther:

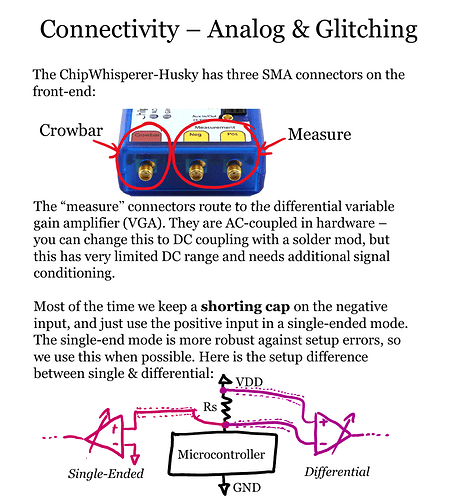

- use a single SMA cable, from Husky’s positive port to the J7 “amplified” port on the target; use the shorting cap on Husky’s negative port

- use two SMA cables: one from Husky positive to the target’s shunt highside, the other from Husky negative to the target’s shunt lowside.

This is explained in the Husky manual: