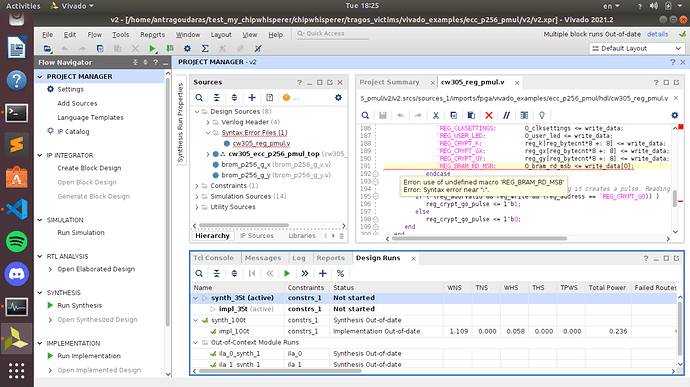

Hello there, the ECC_setup notebook defines the methods for changing to the appropriate bitfiles as defined in this path Bitfiles. However all these bitstreams/bitfiles have been created with impl_100t runs (namely targeting the 100t). I was able to successfully copy the appropriate directory files to recreate my own bitstreams for my Artix 35t version, starting from the “original” project (* ecc_p256_pmul.xpr for Vivado project.*) . However when trying to create the rest of the projects (v2-v5) the following syntax error comes up in the cw305_reg_pmul.v verilog file.

Obviously there is a define missing. If someone could tell me what define value should I assign for the REG_BRAM_RD_MSB I would be grateful, since I am eager to complete all parts of the ECC series tutorials.

Thanks in advance,

Antonios

Hi Antonios,

It’s in the same place as all the other register defines, for example:

./vivado_examples/ecc_p256_pmul/v5/v5.srcs/sources_1/imports/fpga/vivado_examples/ecc_p256_pmul/hdl/cw305_pmul_defines.v

I’m not sure what’s happening here with the v2 build, it’s possible some files got misplaced on the commit. I’ll have to look into that later.

But I have to warn you that you won’t be able to fit all the versions on the a35

Jean-Pierre

1 Like

Once again thank you for your quick response & assistance Jean-Pierre, I guess I am going to take the most reasonable action by replacing the defines for my v2 from v5 and for any others version that also have missing defines or whatever else.

Yeah, probably the a35t has some limitations in terms of LUTs & FFs and other resources, but I guess I have to live with it, but it is fine!

–Antonios

Another question @jpthibault that I had was why is the trace acquisition so slow given we using the CW-lite? So the ADC works with the clock from the CW305 PLL1 @ 50MHZ so given that we capture a adc.sample per clock cycle and let’s say we need 50 traces, I would expect something like this: (20ns {clock period}) * (47 * 24400) * (50) which is approximately one second. (The 47 is the number of segments we need to capture for a single ECDSA given we using 24400 adc.samples). So why is this process takes about 3 minutes in my notebook ?

Is this overhead due to everything else going around the target (reading the samples from the CW-lite usb interface & dispatching other jobs/processes etc)

Exactly - your calculation show the theoretical maximum speed, and to achieve that we’d need to be dumping the power samples straight into your PC’s memory. We would also need to be able to stream those samples, which as you know CW-lite can’t do.

1 Like