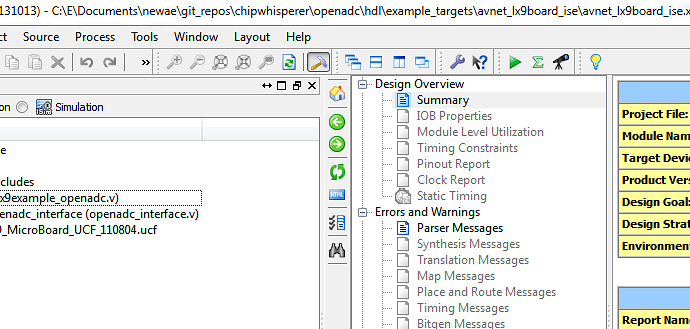

when I run the program, by default the top file is “clock_managment_advanced” That is correct?

It also shows me 3 mistakes, attached below.

error in implementation design—>.MAP

regards,

[code]Started : “Translate”.

Running ngdbuild…

Command Line: ngdbuild -filter “iseconfig/filter.filter” -intstyle ise -dd _ngo -sd coregen -nt timestamp -i -p xc6slx9-csg324-2 “clock_managment_advanced.ngc” clock_managment_advanced.ngd

Command Line: C:\Xilinx\14.7\ISE_DS\ISE\bin\nt\unwrapped\ngdbuild.exe -filter

iseconfig/filter.filter -intstyle ise -dd _ngo -sd coregen -nt timestamp -i -p

xc6slx9-csg324-2 clock_managment_advanced.ngc clock_managment_advanced.ngd

Reading NGO file “C:/Users/EDWARD/Desktop/CODES ADQUISICION/LO

GENERE4-LX9/Avnet_lx9board_ise/clock_managment_advanced.ngc” …

Gathering constraint information from source properties…

Done.

Resolving constraint associations…

Checking Constraint Associations…

Done…

Checking expanded design …

Partition Implementation Status

No Partitions were found in this design.

NGDBUILD Design Results Summary:

Number of errors: 0

Number of warnings: 0

Writing NGD file “clock_managment_advanced.ngd” …

Total REAL time to NGDBUILD completion: 11 sec

Total CPU time to NGDBUILD completion: 11 sec

Writing NGDBUILD log file “clock_managment_advanced.bld”…

NGDBUILD done.

Process “Translate” completed successfully

Started : “Map”.

Running map…

Command Line: map -filter “C:/Users/EDWARD/Desktop/CODES ADQUISICION/LO GENERE4-LX9/Avnet_lx9board_ise/iseconfig/filter.filter” -intstyle ise -p xc6slx9-csg324-2 -w -logic_opt off -ol high -t 1 -xt 0 -register_duplication off -r 4 -global_opt off -mt off -ir off -pr off -lc off -power off -o clock_managment_advanced_map.ncd clock_managment_advanced.ngd clock_managment_advanced.pcf

Using target part “6slx9csg324-2”.

Mapping design into LUTs…

Running directed packing…

Running delay-based LUT packing…

Updating timing models…

WARNING:Timing:3159 - The DCM, DCM_CLKGEN_inst, has the attribute DFS_OSCILLATOR_MODE not set to PHASE_FREQ_LOCK. No phase relationship

exists between the input clock and CLKFX or CLKFX180 outputs of this DCM. Data paths between these clock domains must be constrained

using FROM/TO constraints.

INFO:Map:215 - The Interim Design Summary has been generated in the MAP Report

(.mrp).

Running timing-driven placement…

Total REAL time at the beginning of Placer: 14 secs

Total CPU time at the beginning of Placer: 13 secs

Phase 1.1 Initial Placement Analysis

Phase 1.1 Initial Placement Analysis (Checksum:c626) REAL time: 15 secs

Phase 2.7 Design Feasibility Check

ERROR:Place:1205 - This design contains a global buffer instance, <adcclk_mux>,

driving the net, <systemsample_clk_OBUF>, that is driving the following

(first 30) non-clock load pins off chip.

< PIN: systemsample_clk.O; >

This design practice, in Spartan-6, can lead to an unroutable situation due

to limitations in the global routing. If the design does route there may be

excessive delay or skew on this net. It is recommended to use a Clock

Forwarding technique to create a reliable and repeatable low skew solution:

instantiate an ODDR2 component; tie the .D0 pin to Logic1; tie the .D1 pin to

Logic0; tie the clock net to be forwarded to .C0; tie the inverted clock to

.C1. If you wish to override this recommendation, you may use the

CLOCK_DEDICATED_ROUTE constraint (given below) in the .ucf file to demote

this message to a WARNING and allow your design to continue. Although the net

may still not route, you will be able to analyze the failure in FPGA_Editor.

< PIN “adcclk_mux.O” CLOCK_DEDICATED_ROUTE = FALSE; >

ERROR:Place:1136 - This design contains a global buffer instance, <adcclk_mux>,

driving the net, <systemsample_clk_OBUF>, that is driving the following

(first 30) non-clock load pins.

< PIN: systemsample_clk.O; >

This is not a recommended design practice in Spartan-6 due to limitations in

the global routing that may cause excessive delay, skew or unroutable

situations. It is recommended to only use a BUFG resource to drive clock

loads. If you wish to override this recommendation, you may use the

CLOCK_DEDICATED_ROUTE constraint (given below) in the .ucf file to demote

this message to a WARNING and allow your design to continue.

< PIN “adcclk_mux.O” CLOCK_DEDICATED_ROUTE = FALSE; >

Phase 2.7 Design Feasibility Check (Checksum:c626) REAL time: 15 secs

Total REAL time to Placer completion: 15 secs

Total CPU time to Placer completion: 15 secs

ERROR:Pack:1654 - The timing-driven placement phase encountered an error.

Mapping completed.

See MAP report file “clock_managment_advanced_map.mrp” for details.

Problem encountered during the packing phase.

Design Summary

Number of errors : 3

Number of warnings : 1

Process “Map” failed

[/code]