I noticed my glitches are significantly delayed, around ~800 ns, and I don’t understand why.

I’ve tried to go through all the settings and try them out, but can’t figure it out for simple TIO4 trigger with simpleserial-aes on CW308 target STM32F415 (F3 or ATSAM shouldn’t be different).

This is just slightly modified demo of “02 Husky Triggers” with minimal code to show what’s happening, I’ll add the notebook

husky_glitch_800ns_delay_ipynb.zip (3.5 MB)

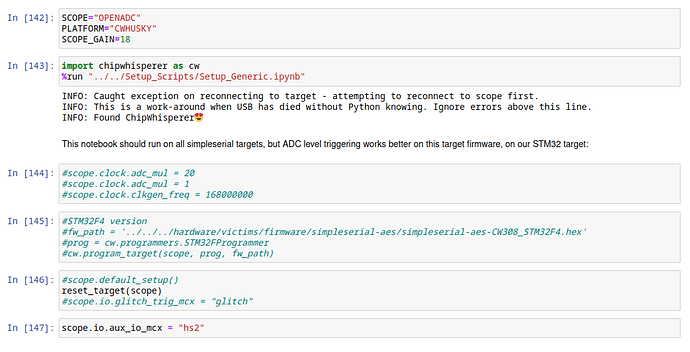

Setup - basic with AUX as HS2 output for oscilloscope

I’ve tried different ADC multipliers, but that didn’t help. Usually clock I need is similar to what CW uses (7.37 MHz or 8 MHz to emulate crystal on board). Program the simpleserial-aes demo for STM32F415.

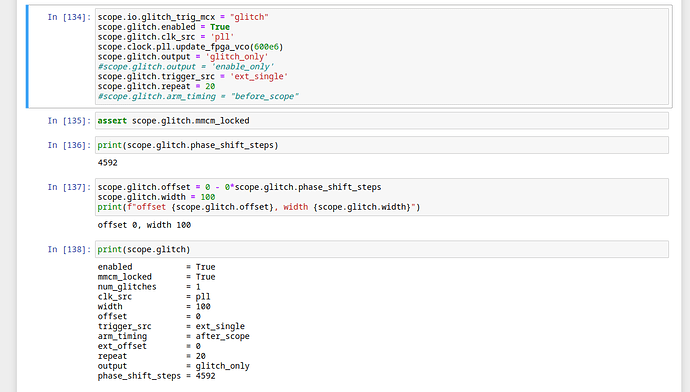

Glitch setup

Tried various settings in the docs, glitch_only/enable_only, changing offsets… according to the glitch network picture

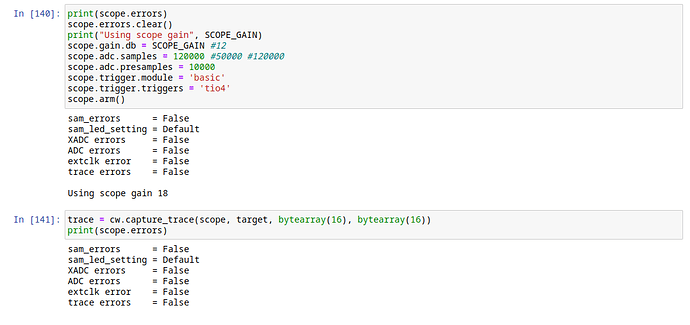

Simple trigger from TIO4 like in demo

Result

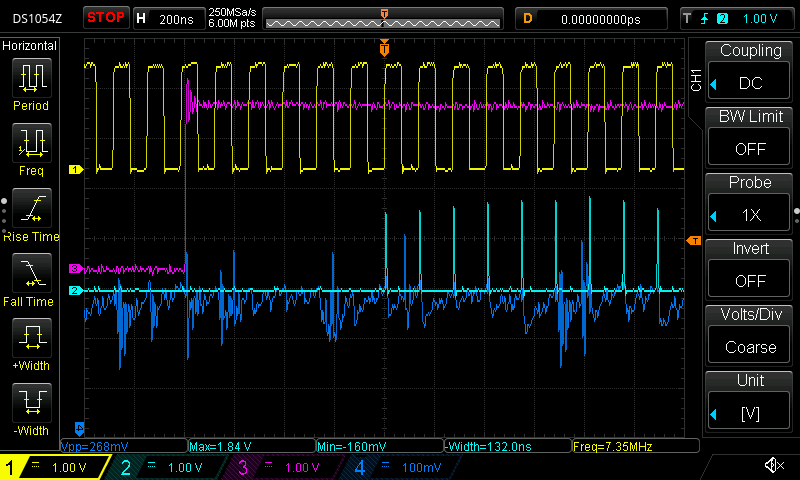

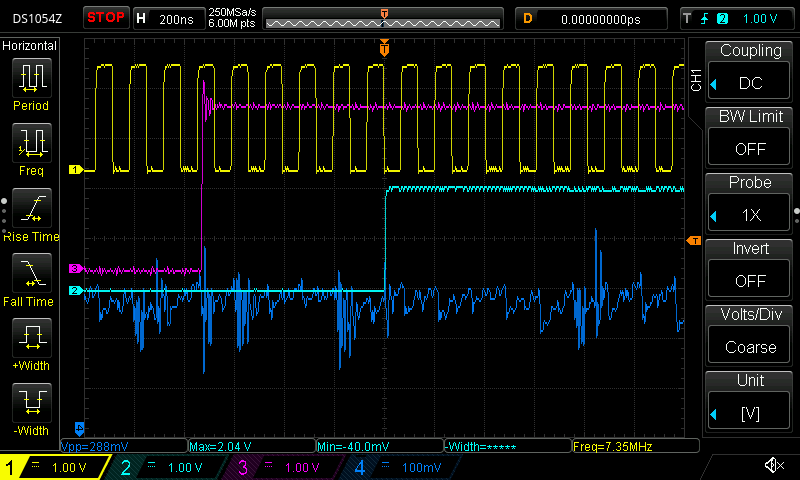

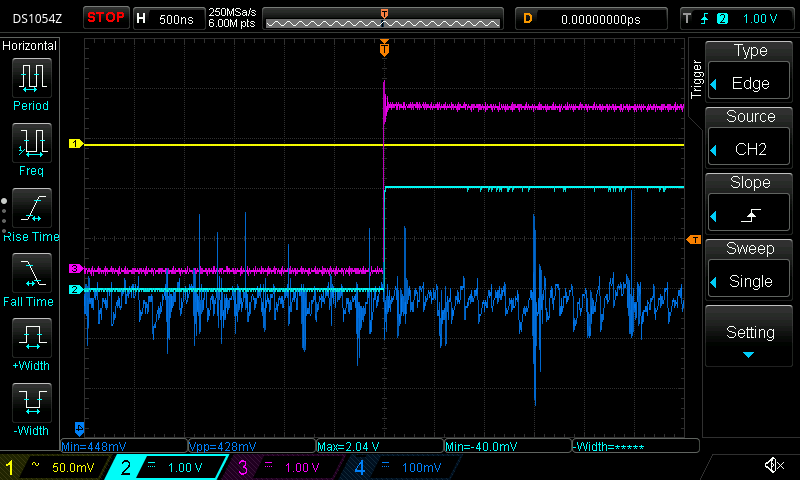

First one is with glitch_only, second one is with enable_only.

- CH1 yellow - HS2 clock from AUX

- CH2 cyan - glitch out

- CH3 magenta - TIO4 trigger

- CH4 blue - from CW501 differential probe

(some signals look a bit dulled since I needed them to terminate with 50 ohm, esp for CW501 to match impedance)

However no idea why the glitch (cyan) comes ~800 ns later than trigger (magenta).

Trigger network part seems right, though

When I switch the Trigger/Glitch out to show trigger, it correctly shows the trigger at about same time as TIO4 (trigger out = cyan, TIO4=magenta)

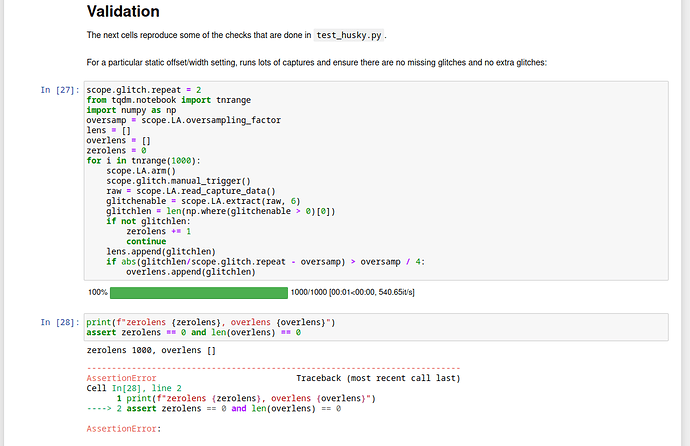

I have no idea where is the bug, since 800 ns is around 1.25 MHz which is very slow. But also the “Validation” part of “03 Husky Glitching” always fails for me, if it might have to do something with it: