Hello everyone,

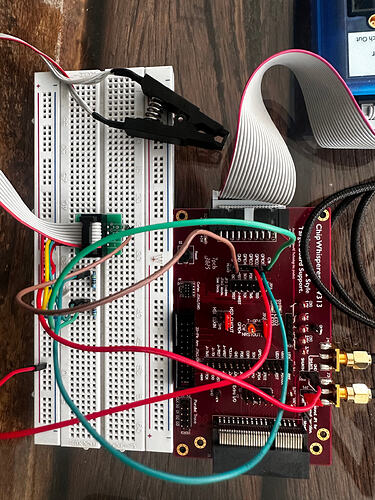

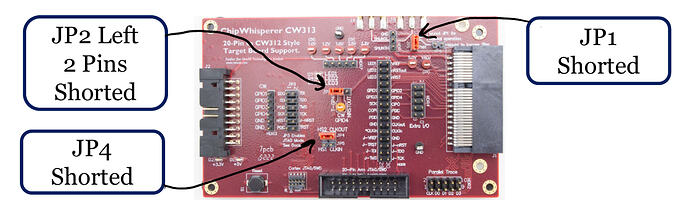

I am a beginner in the SCA field, currently conducting academic research on I2C state-machine behavior using the ChipWhisperer-Husky Starter Kit. I am working with a custom breadboard setup alongside the CW313 Interposer Board.

My research involves analyzing the power consumption of an EEPROM (AT88SC family) during specific I2C transactions. To study the reset state of the chip’s internal logic, my experiment requires power-cycling the target device abruptly before an I2C STOP condition is generated.

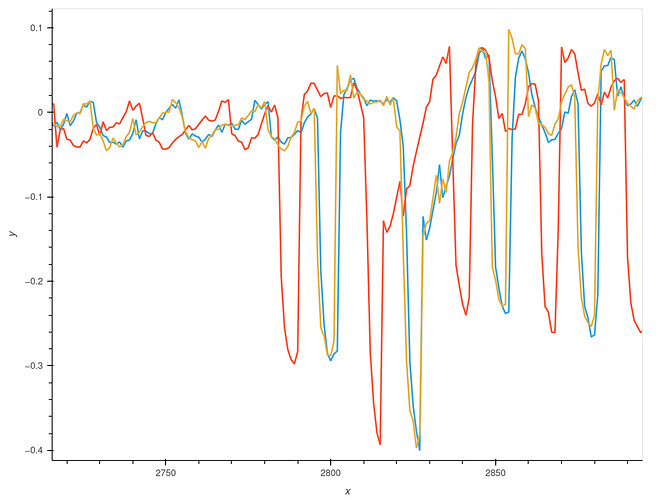

While the logic side of my Python script works, I am facing severe analog and synchronization issues (poor SNR and ghost peaks) and would appreciate some guidance from the community on how to improve my hardware setup.

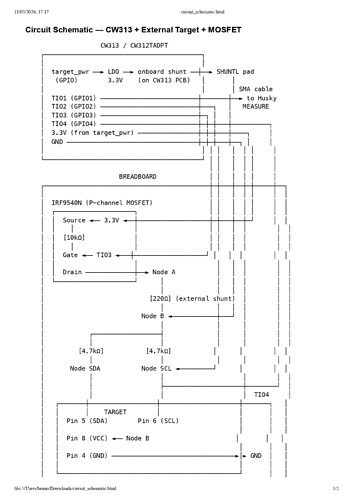

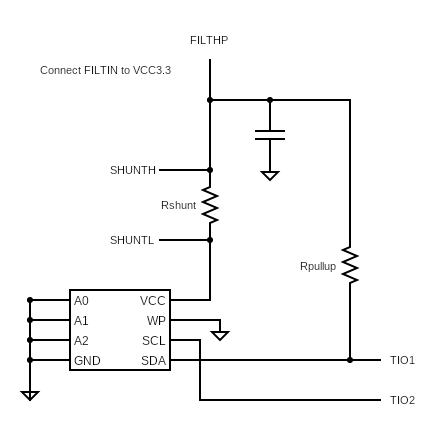

1. Hardware Setup (CW313 ↔ Breadboard)

Since I am bit-banging the I2C protocol, I am using the CW313 to bridge the Husky and my breadboard:

-

Target: 8-lead SOIC connected via micro test clips to a breadboard.

-

I2C Comm: CW313

GPIO01(HuskyTIO1) →SDA| CW313GPIO02(HuskyTIO2) →SCL. -

Pull-up Resistors: Two 4.7kΩ pull-up resistors on

SDAandSCL. I am using CW313GPIO03(driven HIGH via HuskyTIO3) to feed the 3.3V rail powering these pull-ups. -

Power Measurement: I am using the CW313’s onboard shunt. The

SHUNTLpin goes directly to the target’sVCC. I am using Husky’s3.3V Target Power(scope.io.target_pwr) to power the board. Toggling this pin allows me to power-cycle the target.

2. The Analog Problem

Because I am abruptly power-cycling the target during the experiment:

-

Ground Bounce / PLL Issues: When

target_pwris set to False, the resulting ground bounce causes the Husky’s ADC/Glitch LEDs to blink. The FPGA reports target clock issues (even thoughclkgen_src = 'system'). -

Correlation Issues: I am applying FFT alignment on the traces. However, the CPA (Pearson Correlation with Hamming Weight) models are returning erratic peaks (e.g.,

0x12,0x7A). I suspect the power cut transient is completely destroying my SNR, or the bit-banged I2C clock pauses are misaligning the capture window.

3. The Implementation

Here is the core logic I am using. I am arming the scope at the 8th bit of the payload, right before the ACK cycle.

import chipwhisperer as cw

import time

import numpy as np

import scipy.signal

1. SETUP

scope = cw.scope()

scope.default_setup()

time.sleep(0.5)

Shielding the Husky clock for I2C Bit-Banging

scope.clock.clkgen_src = ‘system’

scope.clock.clkgen_freq = 7372800

scope.clock.adc_mul = 4

scope.glitch.enabled = False

scope.clock.reset_adc()

time.sleep(0.5)

scope.errors.clear()

scope.trigger.triggers = “tio4”

scope.trigger.module = “basic”

scope.gain.db = 25

scope.adc.samples = 15000

scope.adc.offset = 0

Power the pull-ups via CW313 GPIO03

scope.io.tio3 = “gpio_high”

def sda(bit): scope.io.tio1 = “high_z” if bit else “gpio_low”

def scl(bit): scope.io.tio2 = “high_z” if bit else “gpio_low”

def i2c_experiment_capture(data_byte):

for i in range(7):

sda((data_byte >> (7 - i)) & 1)

scl(1); scl(0)

sda(data_byte & 1)

scl(0)

# Arm the scope right before the operation

scope.arm()

scope.io.tio4 = "gpio_high"

scope.io.tio4 = "gpio_low"

scl(1)

scl(0)

time.sleep(0.002) # Wait for recording to finish

sda(1); scl(1)

ack = scope.io.tio_states[0]

# Hold SCL low to prevent I2C STOP condition before power cycle

scl(0)

return ack

2. CAPTURE LOOP

num_iterations = 256

traces = np.zeros((num_iterations, scope.adc.samples))

for iteration in range(num_iterations):

temp_traces =

for _ in range(10): # Captures per iteration

scope.io.target_pwr = True

time.sleep(0.05)

sda(1); scl(1)

time.sleep(0.01)

# Standard I2C Start and setup bytes

sda(0); scl(0)

# ... (sending setup bytes) ...

i2c_experiment_capture(iteration)

ret = scope.capture()

if not ret:

trace = scope.get_last_trace()

if trace is not None and (np.max(trace) - np.min(trace)) > 0.01:

temp_traces.append(trace)

scope.errors.clear()

# Power cycle target to study state machine reset

scope.io.target_pwr = False

time.sleep(0.05)

if len(temp_traces) > 0:

traces[iteration] = np.mean(temp_traces, axis=0)

(Standard FFT alignment and CPA math follows…)

My Question: Is this reasoning appropriate for measuring analog data during state-machine interruptions? I would greatly appreciate suggestions from experienced members on how to adjust the Husky ADC settings or improve the hardware measurement to prevent the ground bounce from corrupting the SNR.

Thanks in advance!