Hi all, I am doing side channel analysis for PUF. I am using CWLite and CW305 target board to implement my circuit and trace collection. However, there is a problem in my trace signal. Due to short time executing of my PUF, the trace is 16 values in length by default. So to make my trace is longer, I try to increase the sampling rate of CWLite by changing config as following:

print("SETTING FPGA CLOCKS IN")

target.pll.pll_enable_set(True) #Enable PLL chip

target.pll.pll_outenable_set(False, 0) # Disable unused PLL0

target.pll.pll_outenable_set(True, 1) # Enable PLL

target.pll.pll_outenable_set(False, 2) # Disable unused PLL2

target.pll.pll_outfreq_set(4E6, outnum=1)

print("CLOCK SETUP")

scope.clock.adc_src = "clkgen_x4" #can be clkgen_x1, clkgen_x4, extclk_x1, extclk_x4

scope.clock.reset_adc() # make sure the DCM is locked

scope.adc.timeout = 0.1

#These are only relevant if clkgen (adjustable clock) is being used, if extclk or extclk_x4 is being used these are ignored

scope.clock.clkgen_src = "extclk"

scope.clock.clkgen_mul = 8

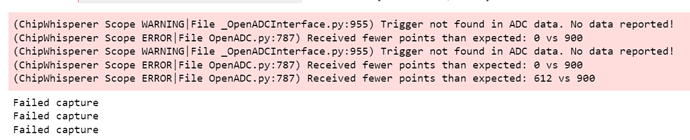

After that, the length of trace is much bigger with 128 values. However, I got the error during collecting data:

Actually, the error is disappeared if I reduce the value of scope.clock.clkgen_mul=4.

Please help me to solve this error, and is there a way to increase the sampling rate of measuring in CWLite?