Hi, I have some problems with voltage glitching.

-

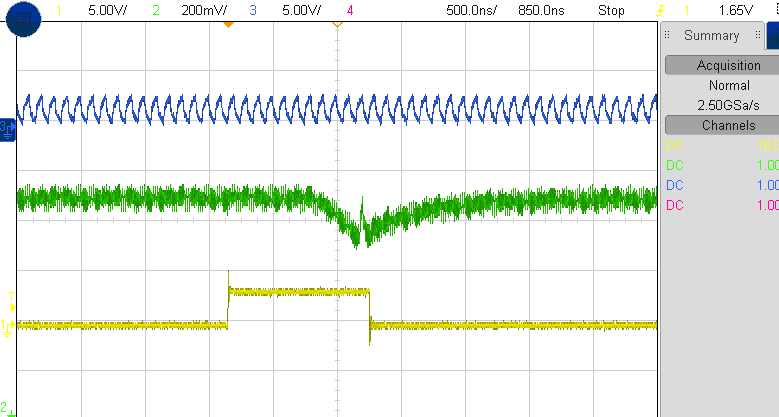

After the trigger, the voltage glitch is not generated immediately but after several clock periods.

-

I adjusted scope.glitch.ext_offset and scope.glitch.repeat, but the attack was still unsuccessful.

I set Input Clock Source to ChipWhisperer HS-IO, and other settings are as follows:

target.vccint_set(0.92) target.pll.pll_enable_set(True) target.pll.pll_outenable_set(False, 0) target.pll.pll_outenable_set(True, 1) target.pll.pll_outenable_set(False, 2) # run PLL1 at 100 MHz: target.pll.pll_outfreq_set(10E6, 1) # 1ms is plenty of idling time target.clkusbautooff = True target.clksleeptime = 1 scope.clock.clkgen_freq = 10E6 scope.glitch.clk_src = "clkgen" scope.glitch.output = "enable_only" scope.glitch.trigger_src = "ext_continuous" scope.io.glitch_hp = True print(scope.glitch) scope.glitch.ext_offset = 1 scope.glitch.repeat = 5

The blue wave is clock signal, the green one is voltage, the yellow one is trigger signal.

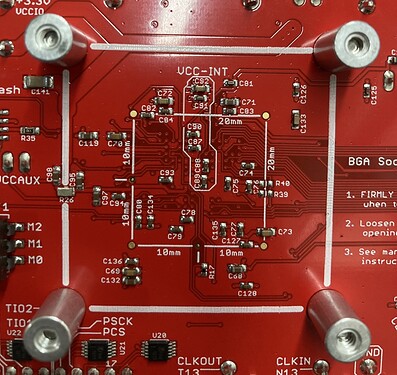

Regarding the second problem above, I think it may be because there is filtering behind the SMA connector X3, so the voltage glitch will not affect the target FPGA. Is it possible to disable the VCC-INT decoupling capacitor on the CW305? Or I’m wrong, there are other reasons I don’t know.

Thank you.