I’m trying to get JTAG / SWD to work with the new STM32F4 WLCSP UFO target daughter board and I am running into some issues:

Programming and verifying works fine, however when OpenOCD tries to run the reset command it fails (see logs below).

At first I was suspecting my JTAG adapter (FT232H), however I now also tried with a ST-LINK V2 and get the same result.

As a sanity check I also tried one of the STM32F3 targets, there it works fine, so I’m pretty sure its not a config or adapter issue.

I’m a bit lost now what could be the cause. I saw that on the bottom of the WLCSP target board there is a Jumper that bridges PA0(WKUP) to nRST. I was wondering whether this might be the cause, but removing it makes OpenOCD already fail at the init phase.

@coflynn Did you try JTAG or SWD programming for the new STM32F4 WLCSP targets yet?

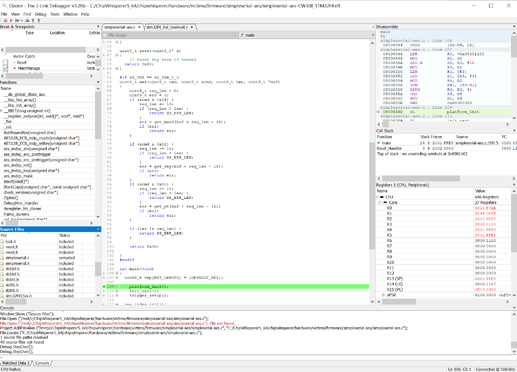

OpenOCD Config and logs

OpenOCD board config

(I reduced the jtag clock because I though it might help, but it doesn’t)

source [find interface/stlink-v2.cfg]

source [find target/stm32f4x.cfg]

reset_config srst_only

adapter_khz 180

OpenOCD log:

(I also have a debug log, but I can’t attach files yet as a new user, and its too long for the post body)

openocd.exe -f cw308.cfg -c "program simpleserial-aes-CW308_STM32F3.elf" -c reset -c shutdown

Open On-Chip Debugger 0.10.0

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : auto-selecting first available session transport "hla_swd". To override use 'transport select <transport>'.

Info : The selected transport took over low-level target control. The results might differ compared to plain JTAG/SWD

adapter speed: 2000 kHz

adapter_nsrst_delay: 100

none separate

srst_only separate srst_nogate srst_open_drain connect_deassert_srst

adapter speed: 180 kHz

Info : Unable to match requested speed 180 kHz, using 125 kHz

Info : Unable to match requested speed 180 kHz, using 125 kHz

Info : clock speed 125 kHz

Info : STLINK v2 JTAG v37 API v2 SWIM v7 VID 0x0483 PID 0x3748

Info : using stlink api v2

Info : Target voltage: 3.643450

Info : stm32f4x.cpu: hardware has 6 breakpoints, 4 watchpoints

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

Info : Unable to match requested speed 2000 kHz, using 1800 kHz

adapter speed: 1800 kHz

in procedure 'program'

in procedure 'reset' called at file "embedded:startup.tcl", line 500

in procedure 'ocd_bouncer'

embedded:startup.tcl:476: Error: ** Unable to reset target **

in procedure 'program'

in procedure 'program_error' called at file "embedded:startup.tcl", line 501

at file "embedded:startup.tcl", line 476