Hi,

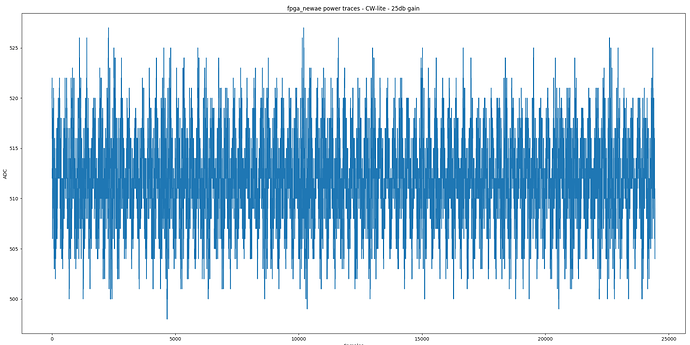

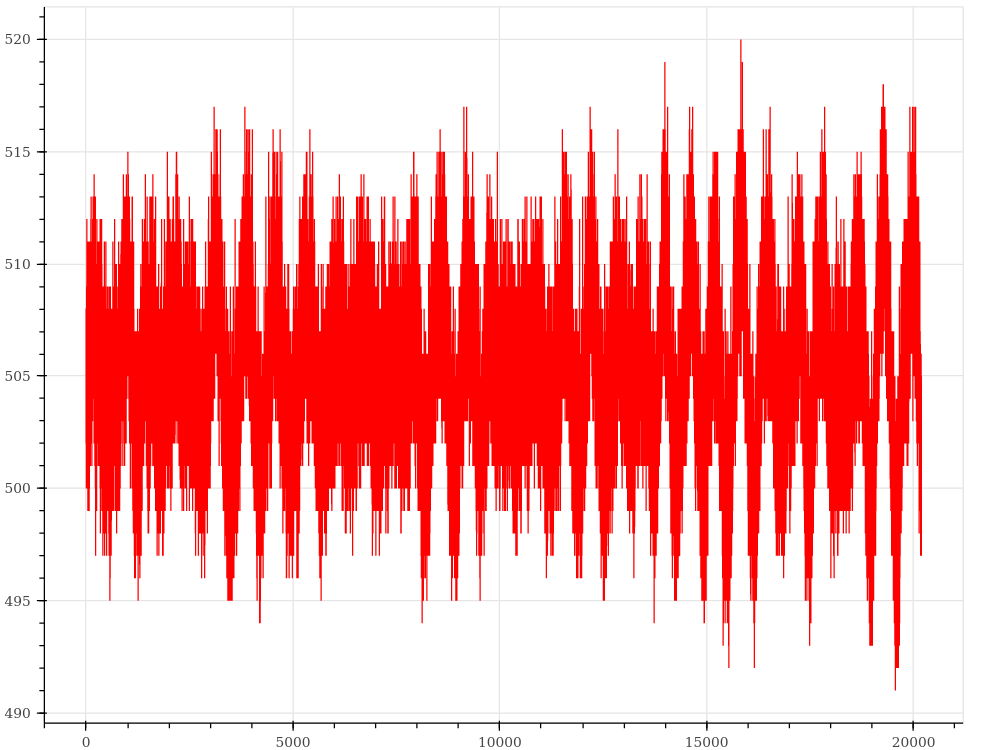

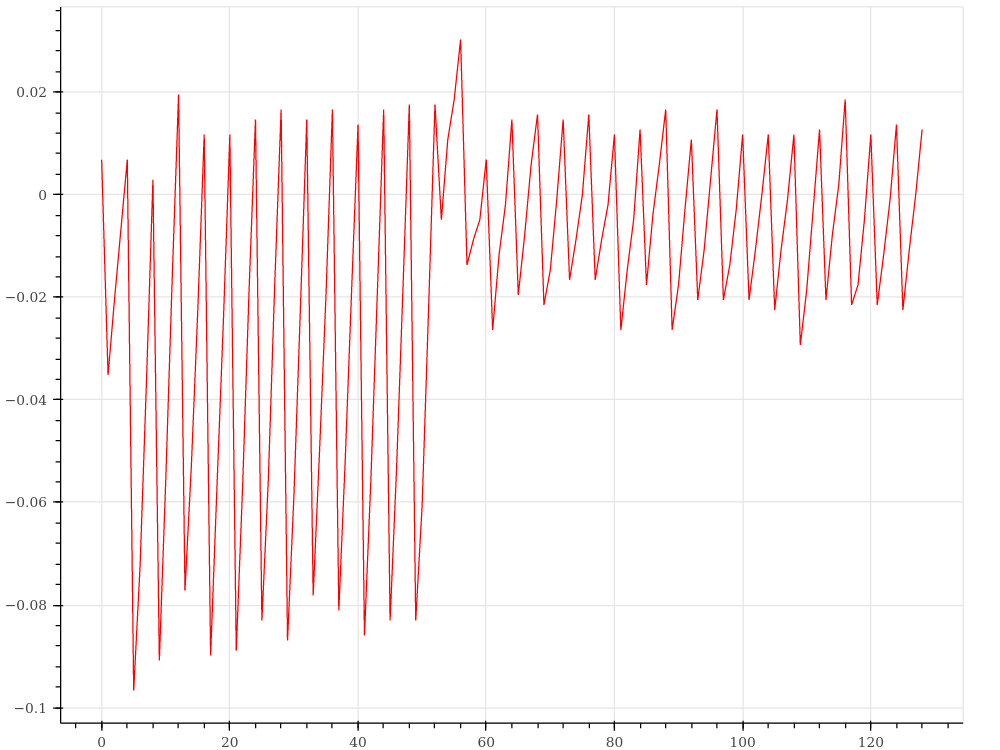

We recently noticed that we were getting fairly low SNR for CW305 measurements. As an experiment, we programmed the FPGA on the CW305 with only a counter instantiated to measure the background noise. We are surprised with the result:

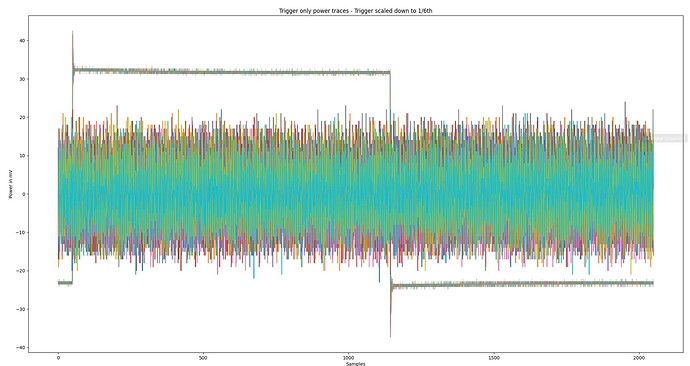

Here we measured 10 power measurements of a counter on the FPGA with a 6000 series PicoScope. The background square signal is the trigger. The power probe is a 10X probe measuring with 100mV/div and AC coupling.

The background noise seems really high (+/- 20mV). We are unsure what could be causing this and if anyone else can replicate it, or if this is expected. Please let me know if you need any additional info/experiments to help debug this!

Here is our verilog HDL for reference:

module cw305_top #(

parameter DELAY = 1000

)(

// USB Interface

input wire usb_clk, // Clock

inout wire [7:0] usb_data, // Data for write/read

input wire [pADDR_WIDTH-1:0] usb_addr, // Address

input wire usb_rdn, // !RD, low when addr valid for read

input wire usb_wrn, // !WR, low when data+addr valid for write

input wire usb_cen, // !CE, active low chip enable

input wire usb_trigger, // High when trigger requested

// Buttons/LEDs on Board

input wire j16_sel, // DIP switch J16

input wire k16_sel, // DIP switch K16

input wire k15_sel, // DIP switch K15

input wire l14_sel, // DIP Switch L14

input wire pushbutton, // Pushbutton SW4, connected to R1, used here as reset

output wire led1, // red LED

output wire led2, // green LED

output wire led3, // blue LED

// PLL

input wire pll_clk1, //PLL Clock Channel #1

//input wire pll_clk2, //PLL Clock Channel #2 (unused in this example)

// 20-Pin Connector Stuff

output wire tio_trigger,

output wire tio_clkout,

input wire tio_clkin

);

wire resetn = pushbutton;

wire reset = !resetn;

reg[32-1:0] delay_counter;

reg trigger_status;

always @(posedge pll_clk1) begin

if (reset) begin

delay_counter <= 0;

trigger_status <= 1;

end else begin

if (delay_counter > DELAY) begin

delay_counter <= 0;

trigger_status <= !trigger_status;

end else begin

delay_counter <= delay_counter +1;

end

end

end

assign tio_trigger = trigger_status;

endmodule