I have another follow-up question.

For Husky and NAE CW312T-A35, when I am printing print(target.platform), it shows ss2_a35 as output.

Is there any way to use cw305_aes.xpr project in this setup? If so, how can I pass the parameters for that?

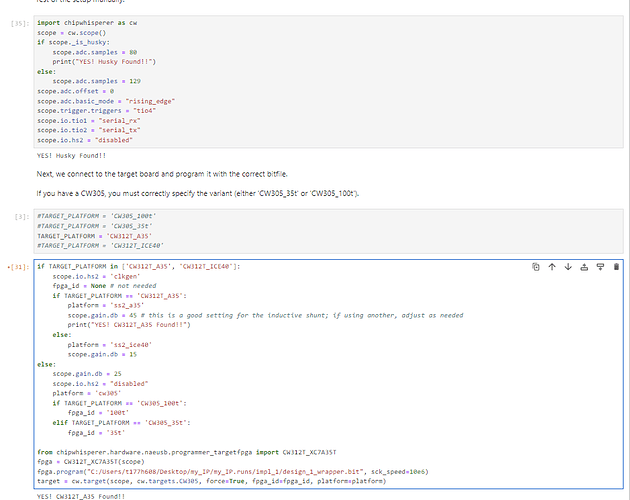

I tried the following script:

scope.io.hs2 = 'clkgen'

platform = 'cw305'

scope.gain.db = 45

fpga_id = '35t'

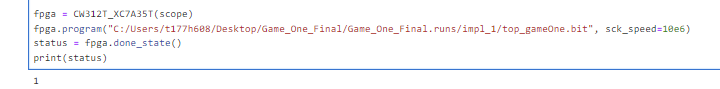

from chipwhisperer.hardware.naeusb.programmer_targetfpga import CW312T_XC7A35T

fpga = CW312T_XC7A35T(scope)

scope.io.hs2 = None

fpga.program("C:/Users/t177h608/SCA/bit_files/cw305_top_A35.bit", sck_speed=10e6)

scope.io.hs2 = 'clkgen'

target = cw.target(scope, cw.targets.CW305, force=False, fpga_id=fpga_id, platform=platform, program=False)

status = fpga.done_state()

print(status)

it is giving me the following error:

--------------------------------------------------------------------------

OSError Traceback (most recent call last)

Cell In[35], line 7

5 fpga.program("C:/Users/t177h608/SCA/bit_files/cw305_top_A35.bit", sck_speed=10e6)

6 scope.io.hs2 = 'clkgen'

----> 7 target = cw.target(scope, cw.targets.CW305, force=False, fpga_id=fpga_id, platform=platform, program=False)

9 status = fpga.done_state()

10 print(status)

File ~\SCA\chipwhisperer\software\chipwhisperer\__init__.py:422, in target(scope, target_type, **kwargs)

407 """Create a target object and connect to it.

408

409 Args:

(...)

419 Connected target object specified by target_type.

420 """

421 rtn = target_type()

--> 422 rtn.con(scope, **kwargs)

424 # need to check

425 if type(rtn) in (targets.SimpleSerial, targets.SimpleSerial2) \

426 and scope and scope._getNAEUSB().check_feature("SERIAL_200_BUFFER"):

File ~\SCA\chipwhisperer\software\chipwhisperer\capture\targets\_base.py:65, in TargetTemplate.con(self, scope, **kwargs)

63 try:

64 self.connectStatus = True

---> 65 self._con(scope, **kwargs)

66 except:

67 self.dis()

File ~\SCA\chipwhisperer\software\chipwhisperer\capture\targets\CW305.py:472, in CW305._con(self, scope, bsfile, force, fpga_id, defines_files, slurp, prog_speed, hw_location, sn, platform, version, program)

470 self.pll = PLLCDCE906(self._naeusb, ref_freq = 12.0E6, board="CW305")

471 self.fpga = FPGA(self._naeusb)

--> 472 self._naeusb.con(idProduct=[0xC305], serial_number=sn, hw_location=hw_location)

473 if not fpga_id is None:

474 if fpga_id not in ('100t', '35t'):

File ~\SCA\chipwhisperer\software\chipwhisperer\hardware\naeusb\naeusb.py:782, in NAEUSB.con(self, idProduct, connect_to_first, serial_number, hw_location, **kwargs)

777 def con(self, idProduct : Tuple[int]=(0xACE2,), connect_to_first : bool=False,

778 serial_number : Optional[str]=None, hw_location : Optional[Tuple[int, int]]=None, **kwargs) -> int:

779 """

780 Connect to device using default VID/PID

781 """

--> 782 self.usbtx.open(idProduct=idProduct, serial_number=serial_number, connect_to_first=True, hw_location=hw_location)

785 self.snum=self.usbtx.sn

786 fwver = self.readFwVersion()

File ~\SCA\chipwhisperer\software\chipwhisperer\hardware\naeusb\naeusb.py:423, in NAEUSB_Backend.open(self, serial_number, idProduct, connect_to_first, hw_location)

417 def open(self, serial_number : Optional[str]=None, idProduct : Optional[List[int]]=None,

418 connect_to_first : bool =False, hw_location : Optional[Tuple[int, int]]=None) -> Optional[usb1.USBDeviceHandle]:

419 """

420 Connect to device using default VID/PID

421 """

--> 423 self.device = self.find(serial_number, idProduct, hw_location=hw_location)

424 if connect_to_first == False:

425 return None

File ~\SCA\chipwhisperer\software\chipwhisperer\hardware\naeusb\naeusb.py:390, in NAEUSB_Backend.find(self, serial_number, idProduct, hw_location)

388 dev_list = self.get_possible_devices(idProduct, attempt_access=(not hw_location))

389 if len(dev_list) == 0:

--> 390 raise OSError("Could not find ChipWhisperer. Is it connected?")

392 # if more than one CW, we require a serial number

393 if hw_location:

OSError: Could not find ChipWhisperer. Is it connected?