Hi!

Currently I am trying to upload an ECB bitstream I have created to my FPGA board. When reading the cipher text that is outputted it is only returning a cipher with 0’s.

Do you have any explanation why this is the case?

Maybe a stupid question but: do i need to change any of the simpleserial files when uploading to FPGA?

Best regards,

Fridthoy

What is your FPGA board? Does your FPGA design implement the simpleserial protocol?

Jean-Pierre

My FPGA-board is the CW305.

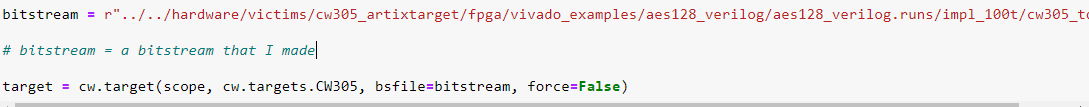

What I am trying to do is to use my own personal bitstream, instead of the one provided by CW. I am working on the file “PA_HW_CW305_1-Attacking_AES_on_an_FPGA”, and I have so far only switched the top line with the commented line:

I do not know exactly how the FPGA design is implemented, but it is done by a colleague who does not have any knowledge of CW. I am not quite sure what you mean by “Does your FPGA design implement the simpleserial protocol?”.

If your colleague kept the register interface used in our reference AES design, then simpleserial is not used (and so to answer your original question: no, you do not need to change anything related to simpleserial).

To debug your FPGA design, I would go through the following steps:

- ensure clocks are alive. If you kept the clock infrastructure from our reference design, you should see two blinking LEDs on the CW305.

- see if you can reliably read/write registers.

- use ILAs to see what’s actually going on.

If you haven’t seen it yet, you / your colleague may find this appnote useful: http://media.newae.com/appnotes/NAE0010_Whitepaper_CW305_AES_SCA_Attack.pdf

Jean-Pierre

1 Like