Hi,

I am analysing my own algorithm while preserving the aes128 vivado example configurations on CW305 and would like to capture both power and EM traces with an oscilloscope (additional to CW-Lite). To trigger the measurements for the oscilloscope, I created a FSM to raise a ready flag/signal.

To which pin on the CW305 I can assign this ready signal as an output?

Are all of the pins on the Expansion header free to use?

Thanks

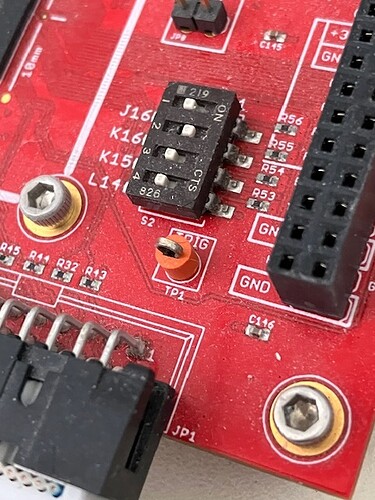

Any unused pin will do, or simply used the existing TRIG TP1 near the lower right corner of the board. It’s connected to IO4.

I couldn’t see anything related to TRIG TP1.

set_property PACKAGE_PIN TP1 [get_ports trig]

Is the above format good to go in the .xdc file? Because I’m getting the following error.

[DRC UCIO-1] Unconstrained Logical Port: 1 out of 45 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: trig.

TP1 is “test point 1”. It doesn’t refer to an FPGA pin; it’s a physical test point that you can access on the board:

It’s connected to the IO4 line of the 20-pin connector; they’re both connected to pin T14. In our reference AES design, this is connected to the tio_trigger signal.

Otherwise you may use any of the signals on the 40-pin header; simply set PACKAGE_PIN to what’s shown on the silkscreen, e.g.

set_property PACKAGE_PIN B12 [get_ports your_verilog_signal_name]